[ad_1]

Why it issues: Moore’s Regulation may not be lifeless in spite of everything. A brand new method utilizing nanomaterials can additional miniaturize transistors, permitting fab vegetation to pack extra of them on every chip. This analysis opens up new prospects for creating superior semiconductor gadgets with options smaller than present lithography methods permit.

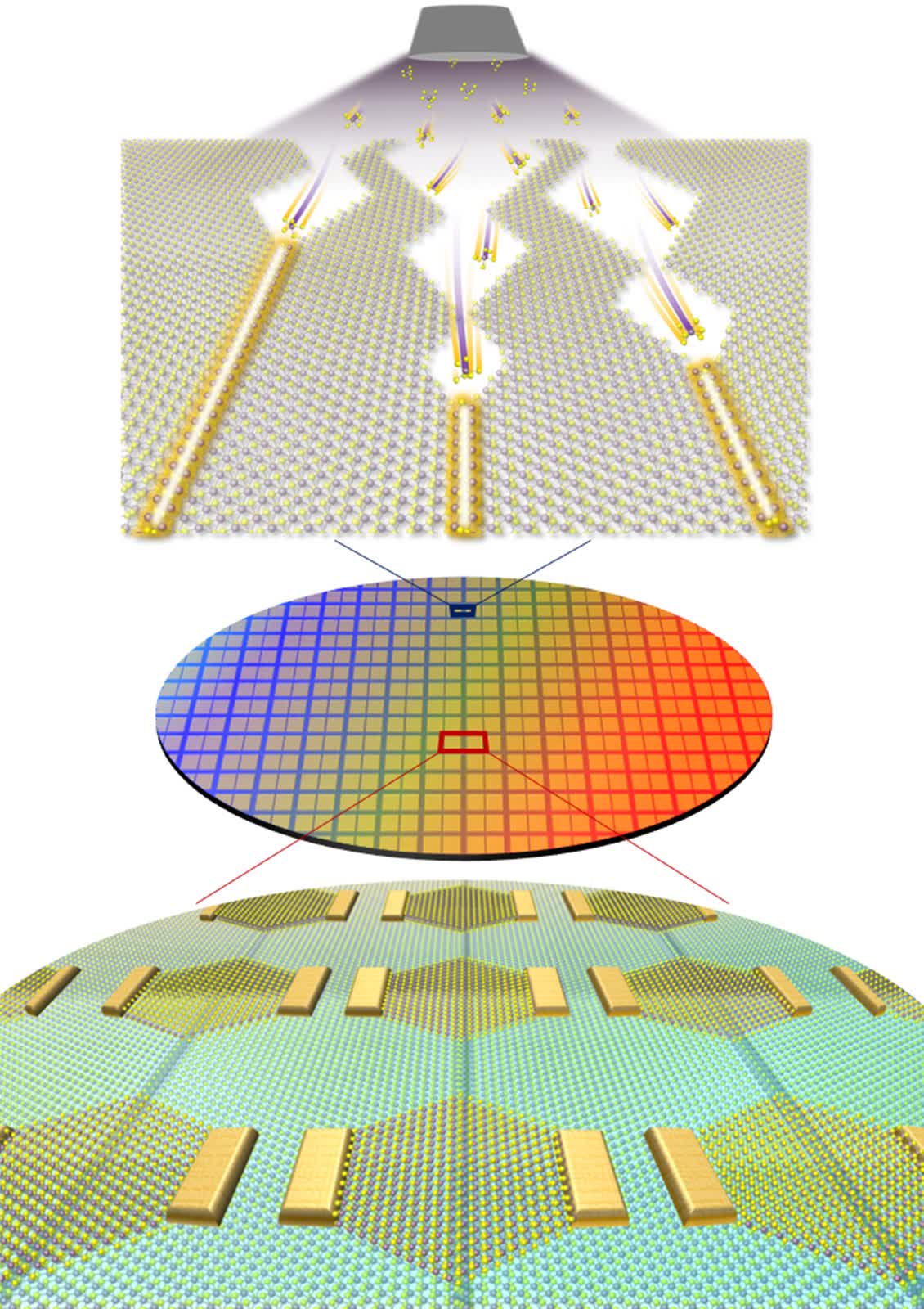

A South Korean analysis group led by Director Jo Moon-Ho of the Heart for Van der Waals Quantum Solids inside South Korea’s Institute for Primary Science has made a big development in semiconductor and nanomaterial know-how that would result in the event of a lot smaller, extra environment friendly, and extra highly effective digital gadgets. The brand new method can develop “one-dimentional” metallic nanaomaterials with widths as slender as 0.4 nanometers to be used as gate electrodes on 2D substrates. The method guarantees to beat the restrictions of conventional lithography.

Built-in gadgets based mostly on two-dimensional semiconductors exhibit glorious electrical properties even when thinned to atomic-scale thickness, making them promising candidates for creating ultra-thin, high-performance digital gadgets. A separate research signifies that these 2D logic circuits are promising candidates for the post-Moore’s Regulation period.

Nonetheless, growing manufacturing processes for built-in circuits based mostly on 2D designs has confronted vital hurdles. Integrating 2D supplies into gadgets with out damaging their delicate construction is extraordinarily troublesome, and reaching constant large-scale manufacturing of high-quality 2D supplies can also be extremely difficult.

One other drawback is that present lithography and fabrication methods do not work at such small scales. In standard semiconductor fabrication processes, lowering the gate size under a couple of nanometers is unimaginable because of the limitations of lithography decision.

It is very important observe that the diploma of integration in semiconductor gadgets is decided by the width and management effectivity of the gate electrode, which controls the circulation of electrons within the transistor. The group leveraged the truth that the mirror twin boundary of molybdenum disulfide, a 2D semiconductor, is a 1D steel with a width of solely 0.4 nm. They used this as a gate electrode, overcoming the restrictions of the lithography course of.

The group may remodel the present 2D semiconductor right into a 1D MTB by controlling the crystal construction on the atomic degree. These 1D metallic buildings can function gate electrodes in ultra-miniaturized transistors.

“The 1D metallic section achieved by epitaxial progress is a brand new materials course of that may be utilized to ultra-miniaturized semiconductor processes,” stated Director JO Moon-Ho. “It’s anticipated to turn out to be a key know-how for growing varied low-power, high-performance digital gadgets sooner or later.”

[ad_2]